## 5<sup>th</sup> Annual eBeam Initiative Luncheon SPIE – February 26, 2013

Aki Fujimura CEO – D2S, Inc. Managing Company Sponsor – eBeam Initiative

3

## eBeam Writes All Chips

#### The eBeam Initiative:

- Is an educational platform for eBeam technology and its impact on all lithography approaches

- Open to any company in the semiconductor design chain with an interest in eBeam technologies

#### **44 Member Companies & Advisors**

## Two Industry Veterans Join as eBeam Initiative Advisors

#### Hugh Durdan Xilinx

## John Chen

## New: The Fine Line Video Journal Use your new earphones!

## **Design for eBeam (DFeB) Roadmap**

#### Roadmap Themes

- Mask write times

- Total cycle times

- Mask accuracy

- Wafer quality

- Design for eBeam Methodology

#### 2010

- Complex masks

- Overlapping shots circles, VSB

- Model-based mask data prep (MB-MDP)

#### 2011

- Thermal analysis of overlapping shots

- Dose control for accuracy

- Double simulation for more accurate analysis of wafer quality

#### 2012

- Mask CD Uniformity improvements

- Accurate measure of mask goodness

- Full chip MB-MDP

#### 2013

- Design for eBeam (DFeB) mask methodology

- Incorporating eBeam Initiative technology roadmap

## Wafer Process Enhanced by eBeam

- More Complex Shapes on mask enhance Wafer Process Latitude

- Complex Masks, Manhattanized or ideal curvilinear, had two problems:

- Poor mask CDU leading to unreliable results on wafer

- Mask write time

- Samsung and GLOBALFOUNDRIES studies show MB-MDP solves this problem

## **Multibeam Technology Progress**

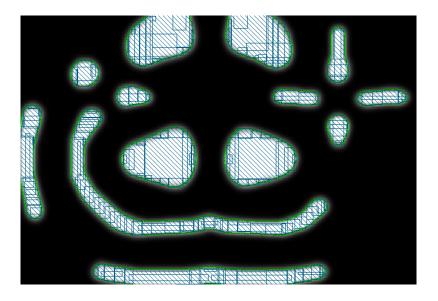

#### eMET POC exposure with 256k-APS

ILT device test pattern

**Design: DNP**

**Scanning Stripe** 20nm beam size exposure

5nm pixel size

ILT device test pattern

with PEC

#### exposure of DNP design

## exposure 2-times smaller

Source: IMS Nanofabrication at BACUS 2012

## **Our Next Speakers**

- Chip Design Perspective

- Hugh Durdan, Xilinx

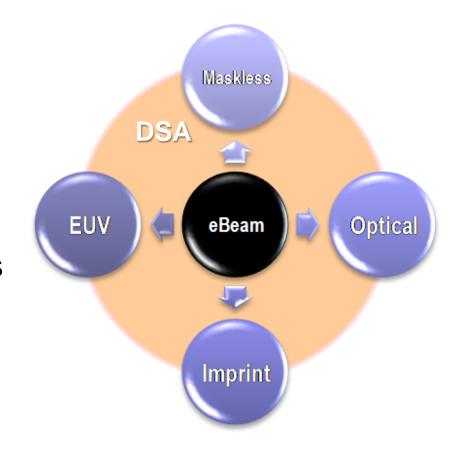

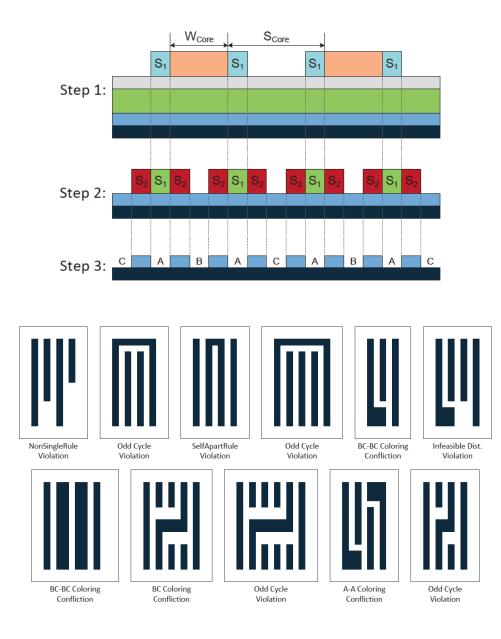

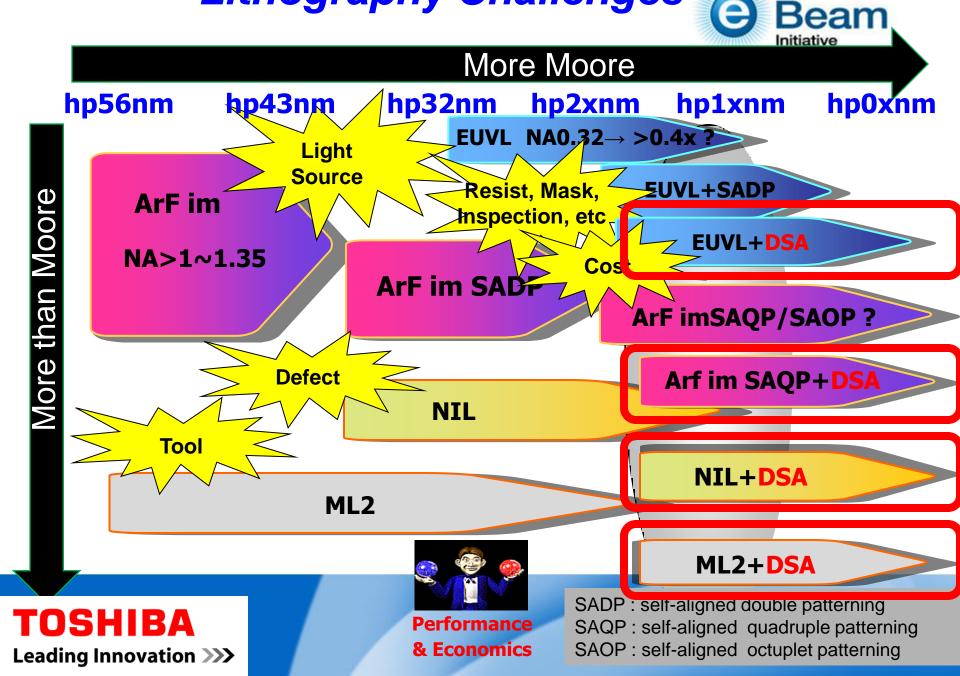

## DSA Technology Challenges

– Dr. Tatsuhiko Higashiki, Toshiba

• Q&A

# **ALL PROGRAMMABLE**

## Lithography Challenges in Advanced Nodes – A Design Perspective

Hugh Durdan Vice President, Portfolio & Solutions Marketing

## **FPGA Characteristics**

#### > Large devices

- -Often > 400mm2

- -Up to 7 billion transistors

### Regular structures

-Ideal for driving process maturation

### Historically benefitted from Moore's Law

- Insatiable demand for more capabilities & capacity

- Until 20nM, process scaling has offered higher performance, lower power, and lower cost at each successive node

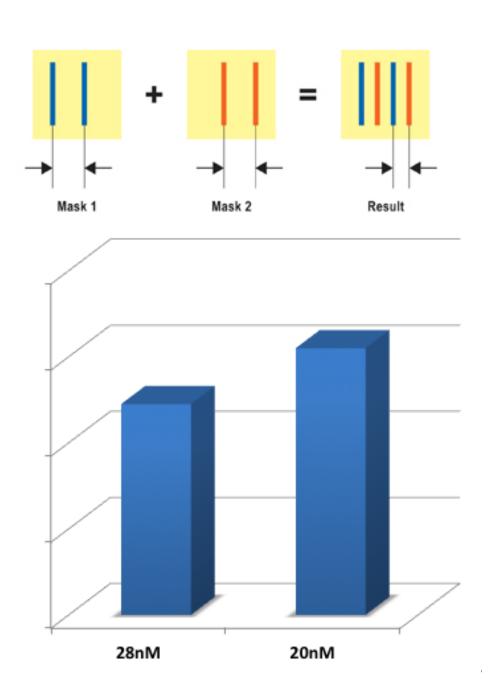

## So What's Changed?

- More complex transistor structure = more masks

- Double patterning required for finer features in 20nM = more masks

- Net result is 30% increase in masking layers

- Directly translates into increased mask and wafer costs

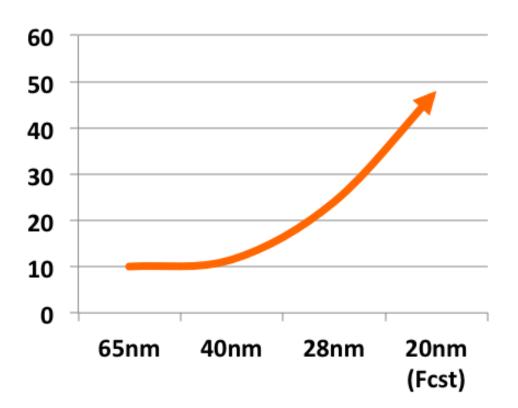

## And Even Worse...

- Mask write time increases exponentially

- Reduced throughput

- Higher cost per mask

- More restrictive design rules

- Larger die

- Reduced CD uniformity

- More design margin

- Lower yields

#### Max. Mask Write Time (Hours)

XILINX > ALL PROGRAMMABLE.

## What Happens at 16/14nM?

## > The Good

- -Higher performance or lower power

- But not both...

## >The Bad

- -Interconnect pitch same as 20nM

- So no die shrink...

## >The Ugly

- -Even more restrictive design rules

- Die size could grow!

- -More mask layers

- Fin-FET structure & double patterning

- -Lower yields

## 10nM & Beyond: Quadruple Patterning

- "Double Double"

- Extends life of existing infrastructure

- 193nM light sources & immersion lithography

- Only a stop-gap for 10nM

- Alignment becomes a significant issue

- Even more restrictive design rules

- More masks = increased mask and wafer costs

#### XILINX ➤ ALL PROGRAMMABLE.

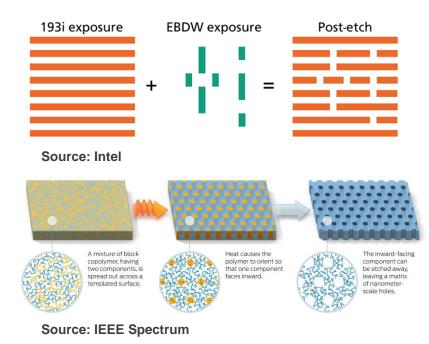

## **Other Possibilities Xilinx is Watching**

> EUV

> Hybrid Approach

Directed Self-Assembly

Source: ASML

Source: KLA-Tencor

XILINX > ALL PROGRAMMABLE.

## **Perspectives**

- Lithography challenges are a significant threat to maintaining Moore's Law

- Cost per transistor is going up for the first time in the history of the semiconductor industry

#### > No good solution on the horizon

- Quadruple patterning only good in the short-term

- -EUV immature, expensive, and late

- Direct-write too slow today for volume production

#### Beam will be part of the solution

- Better accuracy in mask making to reduce CD variation

- Hybrid approach

- Direct write if throughput can be improved

## DSA Technology Challenges

Center for Semiconductor Research & Development Advanced Lithography Process Technology Dept.

Tatsuhiko Higashiki

## Lithography Challenges

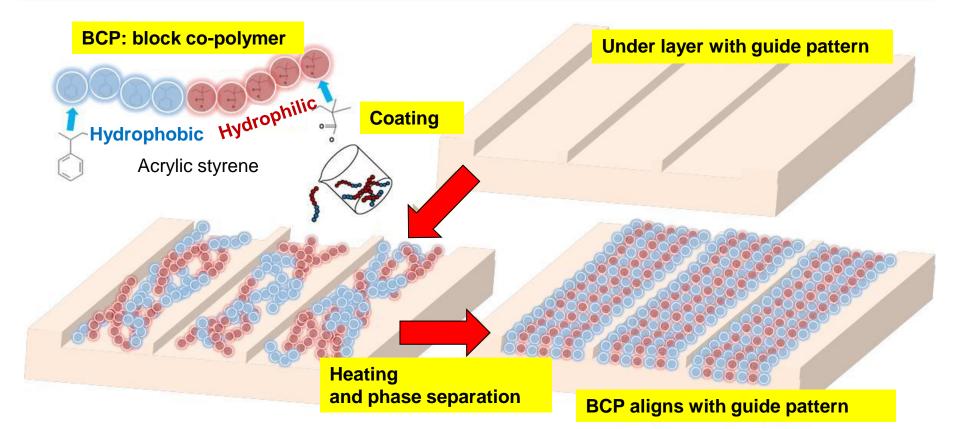

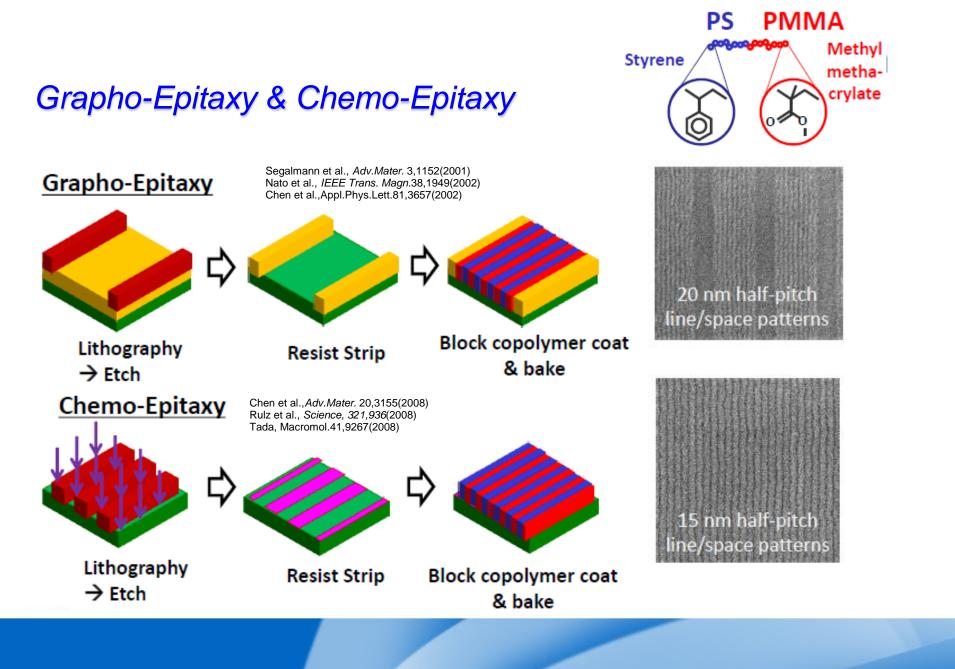

## DSAL (Directed Self Assembly Lithography) @ Beam

#### Lithography of using self-organization phenomenon of polymer

Initiative

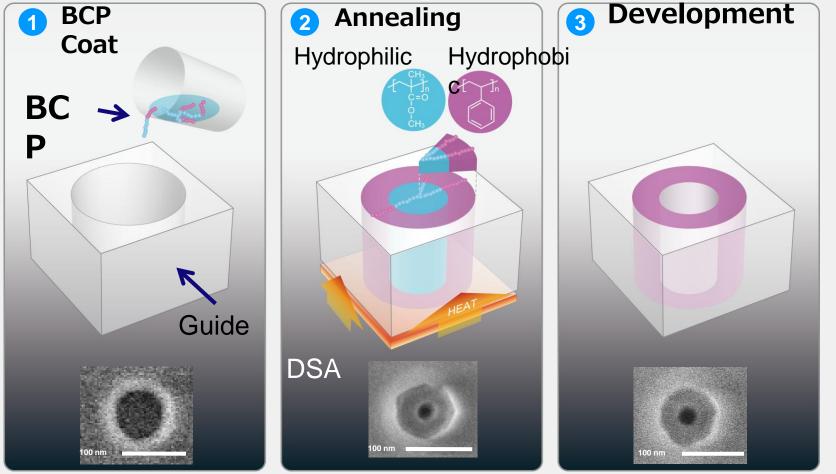

## DSA L for Contact Hole Pattern

#### Process Flow of DSA Lithography BCP Annealing

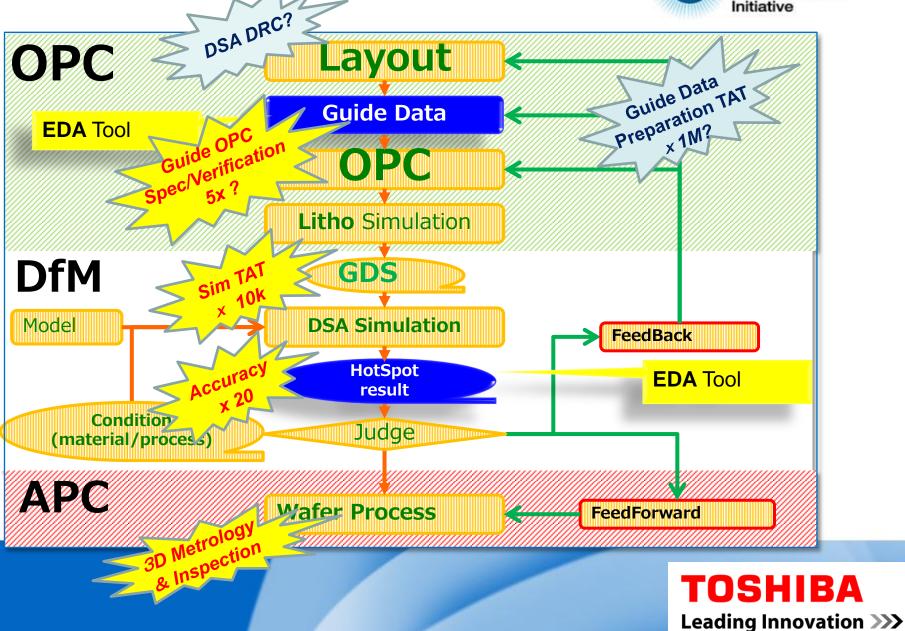

## DSA OPC/DfM/APC Flow

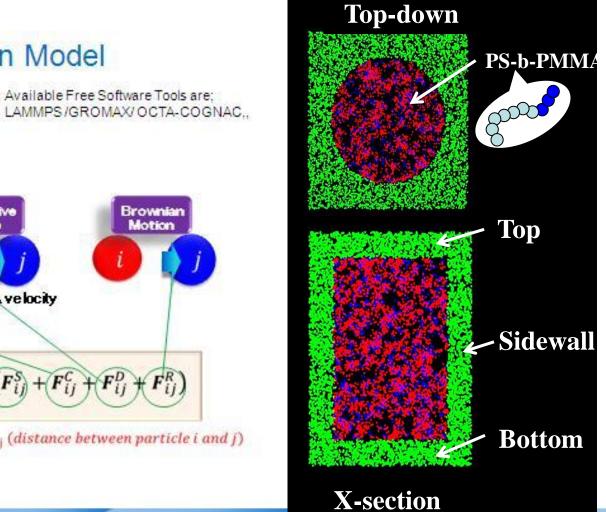

## **Example of DPD Simulation**

#### **TOSHIBA** Leading Innovation >>>

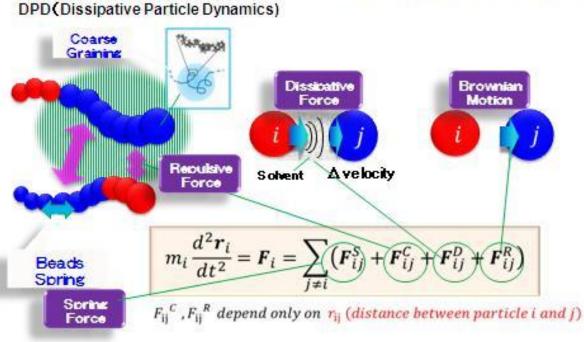

#### **DSA Simulation Model**

Molecular Dynamics

Coarse Grained Model by

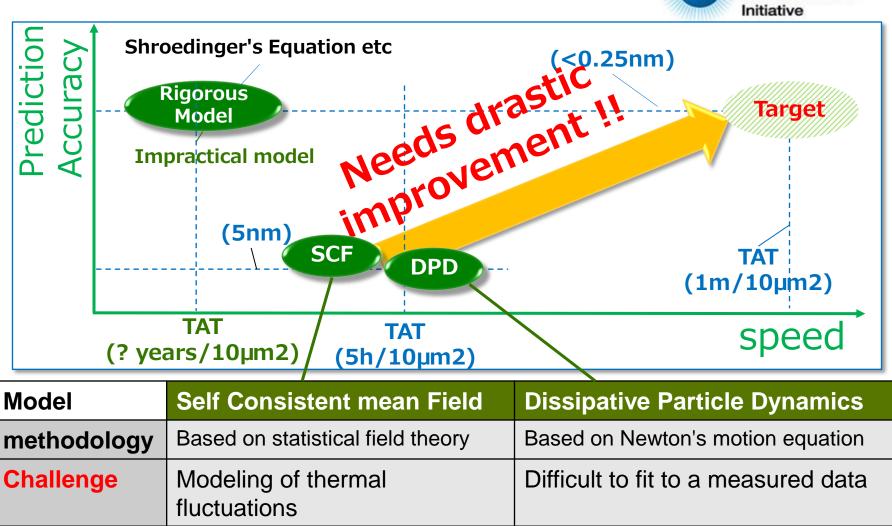

## **DSA Simulation Model**

## **Conclusion: Challenges for DSAL** Beam

- High performance DSA material

- Resolution, LWR/LER, Etching

- Long term stability

- Robust material and tool for environmental control such as surface energy stability, temperature, humidity, pressure and PH, etc.

- Defectivity, CD and overlay accuracy

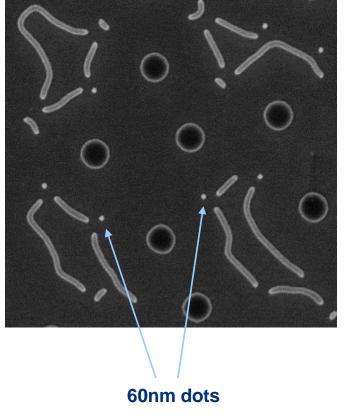

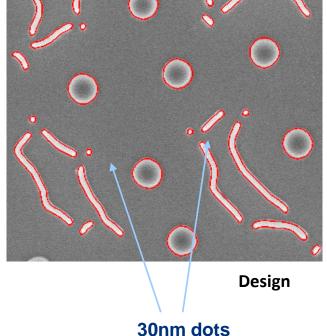

- Metrology & Inspection

- Metrology for 3D profile

- Inspection technology for 1xnmhp and beyond needs to overcome t-put vs accuracy/sensitivity trade-off.

- Development of molecular dynamics based DSA simulator

- More accurate simulation model

- BCP and related molecular design

- Microphase separation (2D/3D)

- DSA and guide patterning (litho/wet/dry)

- TAT vs accuracy trade-off

- DSA OPC/DFM technology

- Design rule verification

## **TOSHIBA** Leading Innovation >>>

2013/2/26

## Q & A

30