# Curvilinear Masks in Memory Designs: From DUV to EUV

Ezequiel Russell Senior Director of Mask Technology September 27, 2022

© 2022 Micron Technology, Inc. All rights reserved. Information, products, and/or specifications are subject to change without notice. Micron, the Micron logo, and all other Micron trademarks are the property of Micron Technology, Inc. All other trademarks are the property of their respective owners.

### Outline

- Enabling DRAM and NAND scaling roadmaps

- A case for curvilinear masks to extend DUV multi-patterning

- EUV curvilinear masks need

- A DRAM array example

- Conclusions

## Scaling Challenges

Advanced technology nodes face increasingly complex and disruptive scaling challenges

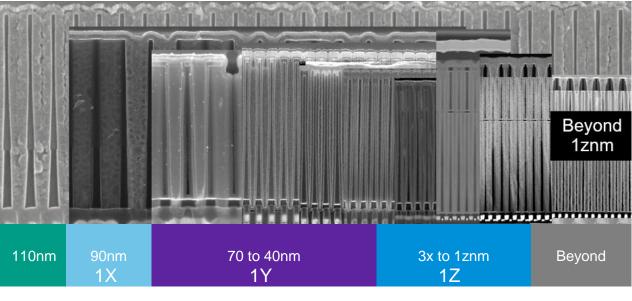

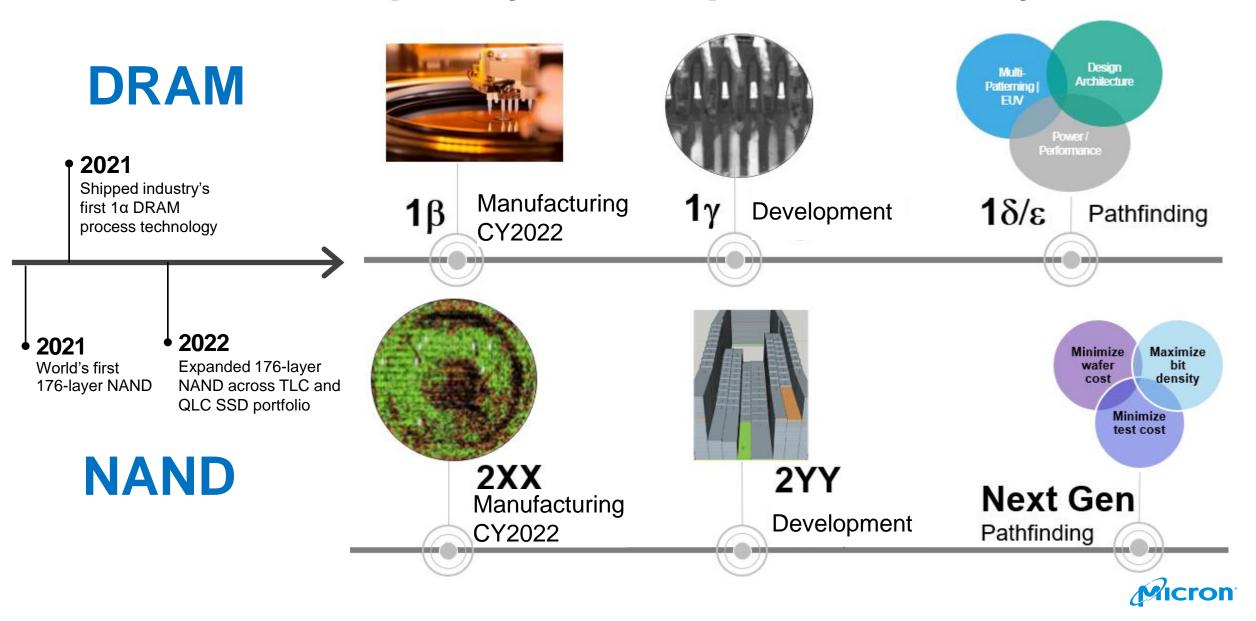

#### DRAM

Advanced patterning: EUV, multi-patterning Structural and material innovations required to meet performance and power requirements

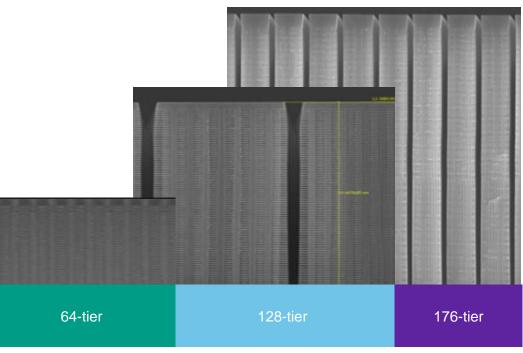

#### NAND

Cost scaling and accelerated performance improvements required

#### Micron Roadmaps beyond 1-alpha and 176 layers

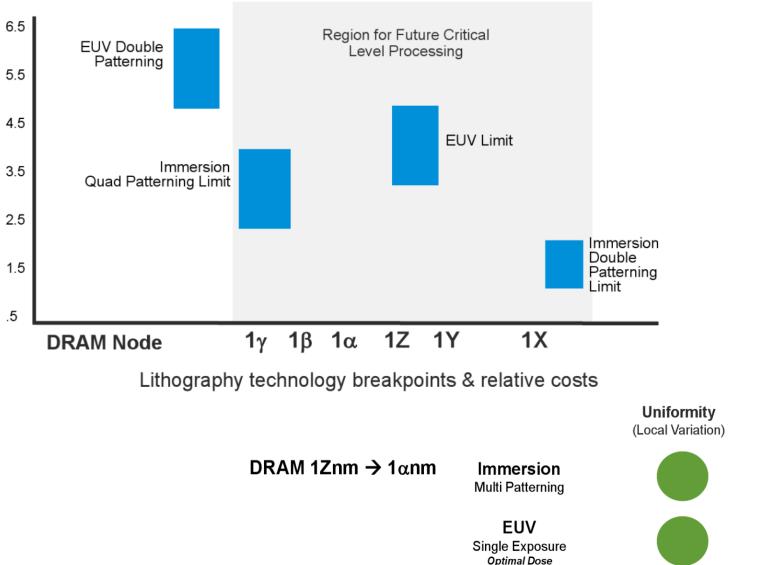

### **Extending DUV Multi-Patterning**

#### **Cost Compared to Immersion**

**Cost Multiple**

Micron's pattern multiplication is a strategic advantage

June 2021 Micron announced EUV adoption for advanced nodes in development

Continue to extend DUV multipatterning in advanced DRAM and NAND nodes

Co

# Extending Optical (DUV) Lithography

#### 1-alpha DRAM and 176-layer 3DNAND

- -Using optical multi-patterning lithography

- Extend RET and OPC techniques to extract achieve process window

#### Enablers

- ILT: Curvilinear and stepped-Manhattan masks

- -Model-based retargeting  $\rightarrow$  Curvy designs

- Efficient use (and reconstruction) of hierarchy for manageable cycle time for ILT

## Why Curvilinear Masks

#### More degrees of freedom for OPC solutions

- Assist features: improved process window, optimal placement

- -Main features: infinitesimally small segmentation of OPC, higher degree of control of the correction

- -Physically meaningful MRCs (no corner-to-corner)

- -Accurate target representation for Mask and Wafer

#### Mask Fidelity

- Improved matching between mask and intended OPC shapes

- -More accurate OPC models

- No need to compensate for differences between "intended" shape and mask shape

- Mask friendly shapes (no sharp corners)

- Mask uniformity: reduces variations at feature corners

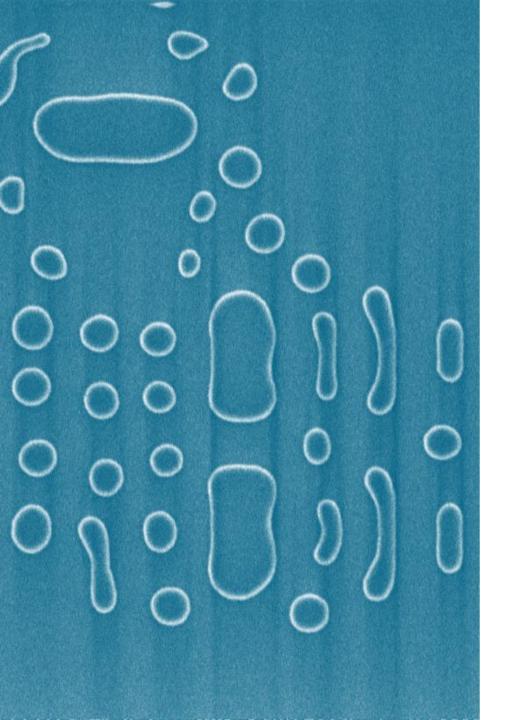

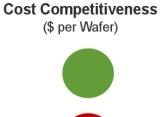

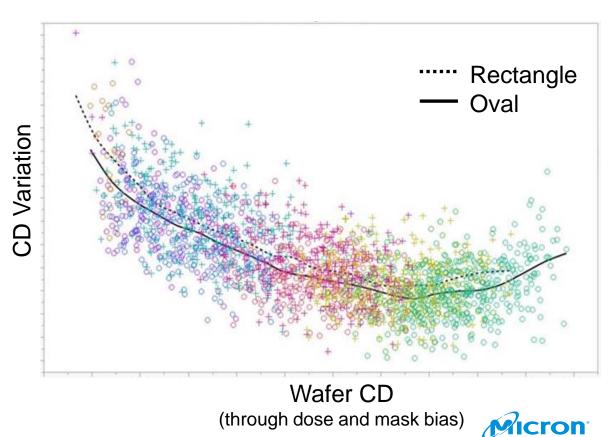

### **Curvilinear Masks: DRAM Array Layer**

Mask SEM

Mask Data

- Curvilinear DRAM Array shapes produced visually more consistent shapes

- Wafer CD Uniformity shows a ~10% improvement for curvilinear mask

## **Application of ILT and Curvilinear Masks**

#### ILT is the ultimate OPC algorithm

- Starts from the intended wafer image to calculate the mask to produce that image

- Naturally includes assist features

- Pixel based solution, intrinsically curvilinear

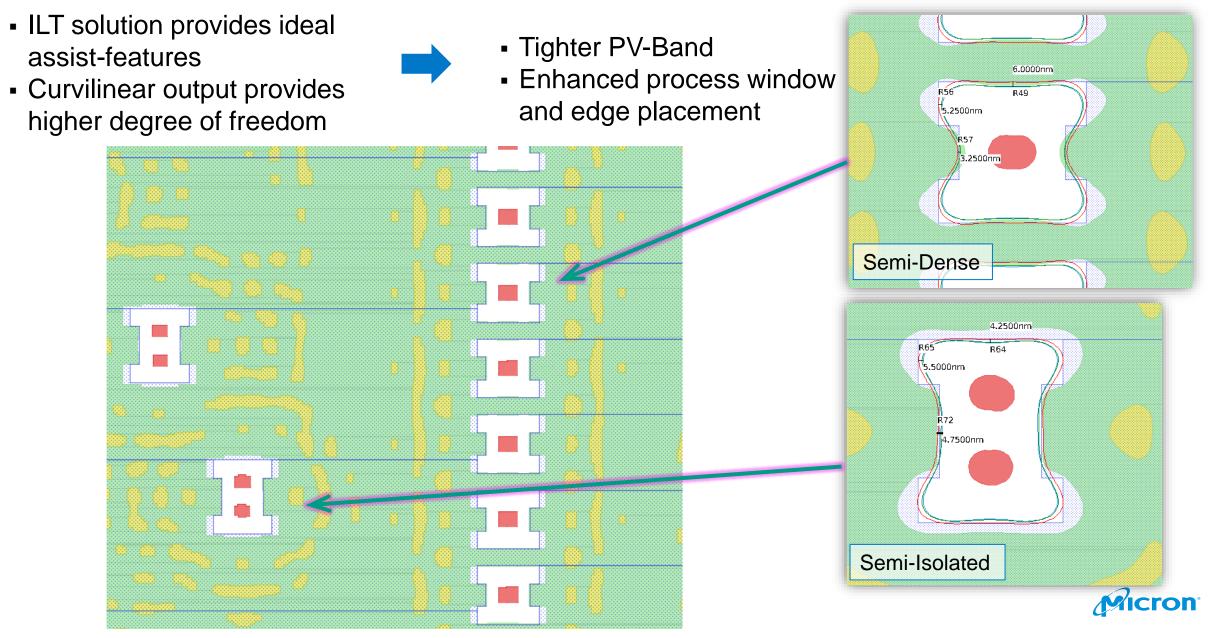

#### ILT OPC improves process window and accuracy

- Optimal assist feature placement

- Increased accuracy: solution is calculated in every point, not just few evaluation points

- Computationally intensive: full-chip processing times were prohibitive

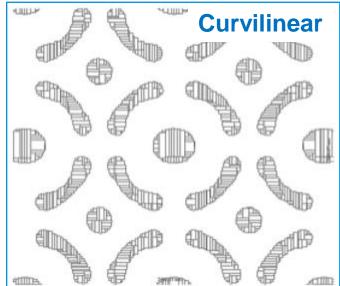

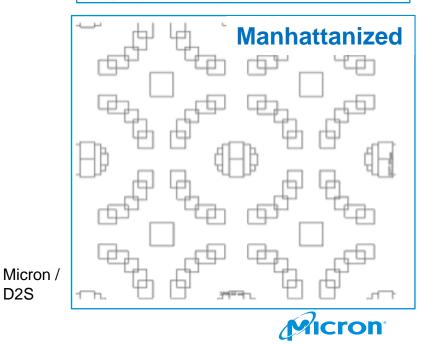

- Curvilinear masks had to be approximated by stepped polygons to write them (Manhattanization)

- Enablers today:

- Higher computation bandwidth: GPUs and faster CPUs

- Multi-beam mask writers make full curvilinear masks possible

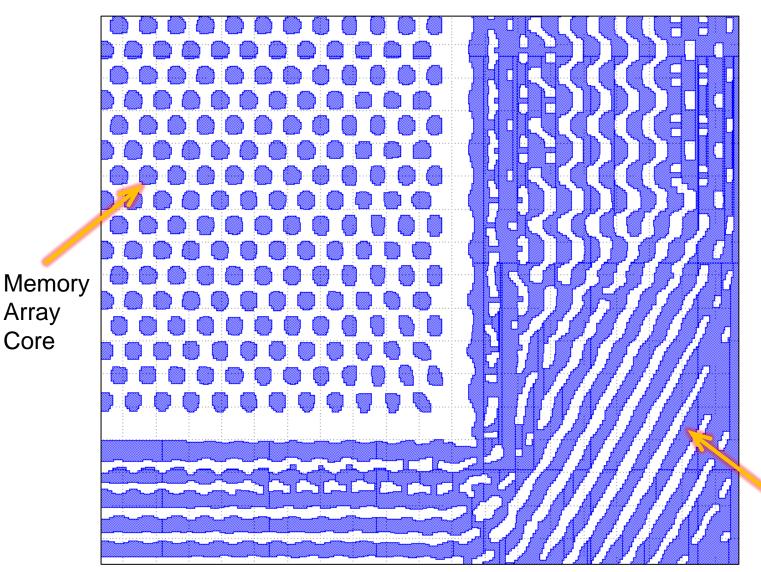

### **DRAM Array Core: Curvilinear ILT Correction**

Improved NILS, CD Uniformity, and Contact Shape

#### Full-Chip ILT

- Application to a common

DRAM array contact-like layer

- CD uniformity and contact shape is critical

#### Mask Complexity

Both Main features and assist features are curvilinear (small step Manhattanized) ILT

Assist Features (SRAFs)

### **ILT and Conventional OPC Blended**

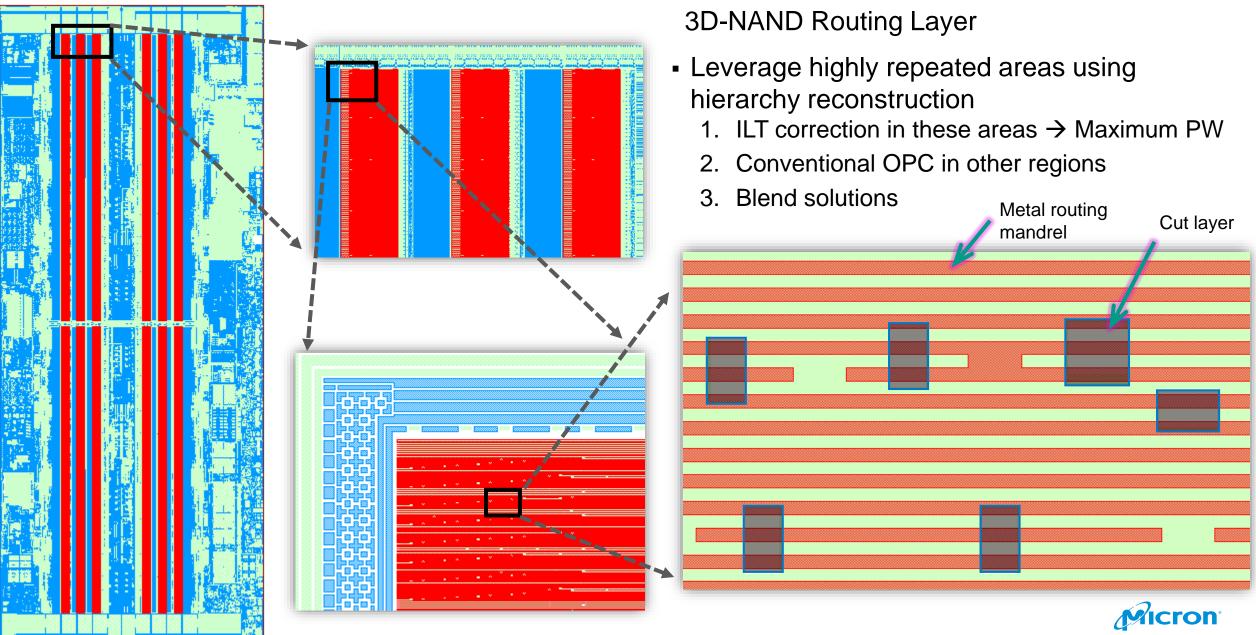

### **3D-NAND Multi-Patterning Routing Layer**

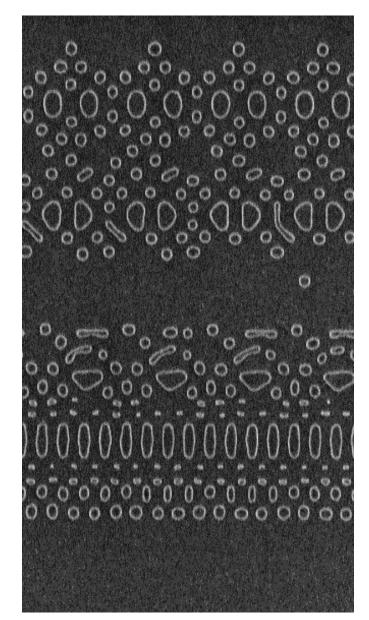

# **Curvilinear EUV Masks Need**

#### A case for Curvilinear EUV Masks

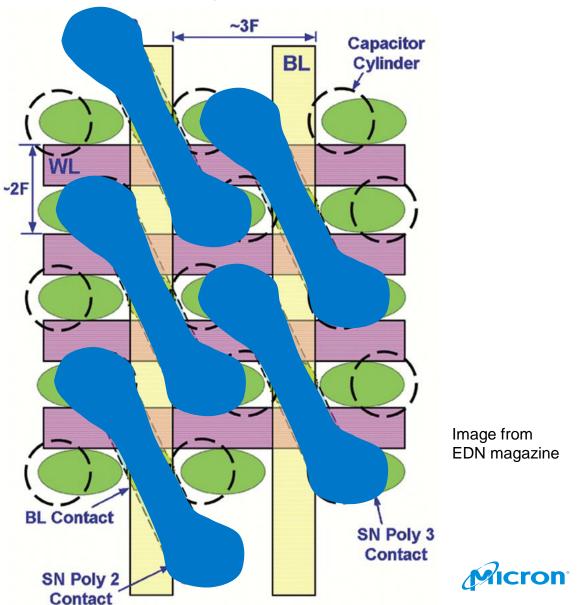

Typical 3x2F DRAM cell architecture

## A case for Curvilinear EUV Masks

- EUV used in next DRAM nodes to pattern critical layers

- Leverage higher EUV resolution <u>now</u>

- DRAM array: Maximize cell contact and device performance

- More complex target shapes to maximize to make use of available area

- Define target as real wafer desired target to apply EUV-OPC

- Multi-beam writer required / Challenges:

- Large data volume

- How to efficiently apply MPC to incoming?

- High data density

- Flattened field data due to EUV OPC

- Standard file format for Curvy data

Typical 3x2F DRAM cell architecture

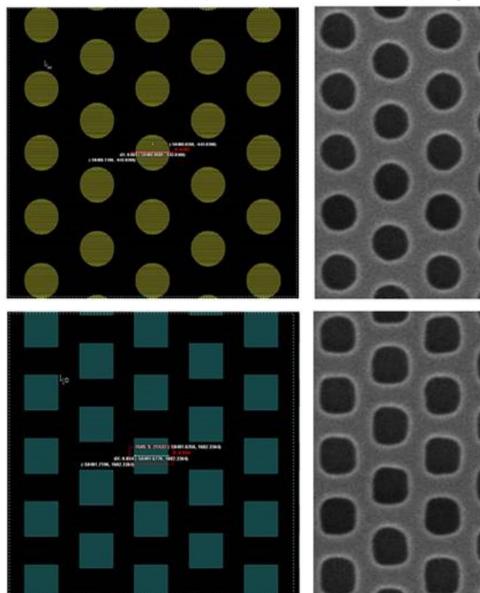

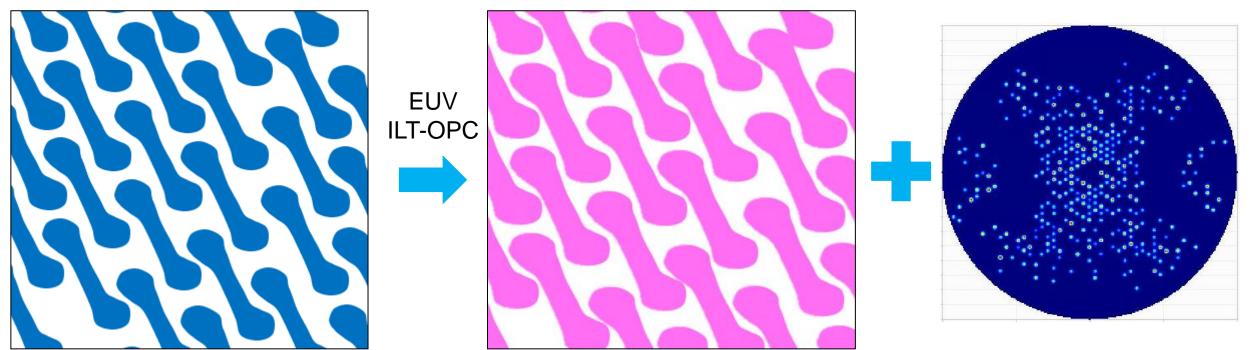

## **EUV Curvilinear Optimization Flow**

Curvilinear Wafer Target

Curvilinear Mask

Curvilinear Optimized Source

- Benefits

- Ideal shape on wafer

- Unconstrained ILT solution

- Maximum process window

#### Conclusions

- Case for curvilinear masks and unconstrained OPC as an enabler to extend DUV multi-patterning

- Curvilinear mask shapes improve OPC model accuracy and help achieve a more uniform mask

- EUV curvilinear masks can be used to extend 0.33NA EUV tools but also to capitalize on additional resolution to pattern more complex shapes to improve memory design and performance

- Multi-beam writers required for large scale curvilinear mask

- Infrastructure needs to be advanced for supporting a full curvilinear tapeout flow